The Critical Issue of Near Holes in Multi-Layer PCB Design

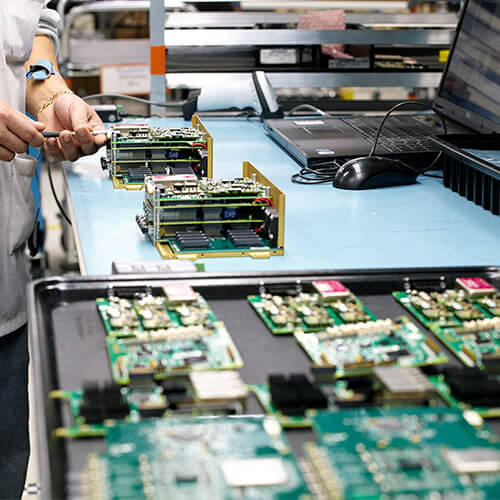

In multi-layer PCB design, the primary focus during routing is to ensure efficient and reliable electrical connections between layers using vias. However, as PCB density increases, vias often need to be placed closer together, leading to design and manufacturing challenges. These challenges not only complicate the production process but also impact the long-term reliability of the product. This article explores the issues caused by closely spaced vias and provides guidelines to mitigate them.

Challenges of Closely Spaced Vias in PCB Design

- Drilling Process Limitations:

- When two holes are placed too close, drilling precision is compromised. After the first hole is drilled, the material near the second hole becomes too thin. This causes:

- Uneven stress and heat distribution on the drill tip.

- Increased likelihood of drill tip breakage.

- Hole collapse, poor appearance, or incomplete drilling.

- When two holes are placed too close, drilling precision is compromised. After the first hole is drilled, the material near the second hole becomes too thin. This causes:

- Hole Ring and Line Proximity:

- In multi-layer boards, vias have hole rings on each layer. The proximity of hole rings to lines can vary depending on the surrounding environment:

- Tight spacing: CAM engineers may need to reduce the hole ring size to maintain a safe clearance of 3mil between the solder ring and adjacent copper or wires.

- Example Issue: If the distance between the hole edge and line edge is 6mil and the hole ring is 4mil, the remaining clearance to the line is only 2mil, requiring optimization.

- In multi-layer boards, vias have hole rings on each layer. The proximity of hole rings to lines can vary depending on the surrounding environment:

- Drilling Tolerance Issues:

- Drilling tolerances (up to 0.05mm) can lead to the following:

- Pad Cutting: Tight spacing results in irregular pad cutting to maintain the required clearance, reducing the solder ring size.

- Risk of Breakage: Pads can shrink to as small as 3mil, and further deviations may break the solder ring entirely.

- Drilling tolerances (up to 0.05mm) can lead to the following:

- Lamination Deviations in Multi-Layer Boards:

- Inner layer misalignment during lamination introduces additional irregularities:

- Deviations of ≤0.05mm can shift hole positions in 360° directions.

- Combined with reduced solder rings, this can lead to compromised hole integrity.

- Inner layer misalignment during lamination introduces additional irregularities:

- Impact on Reliability:

- While initial electrical tests may pass, vias with inadequate copper protection are prone to failures over time, particularly in high-stress environments.

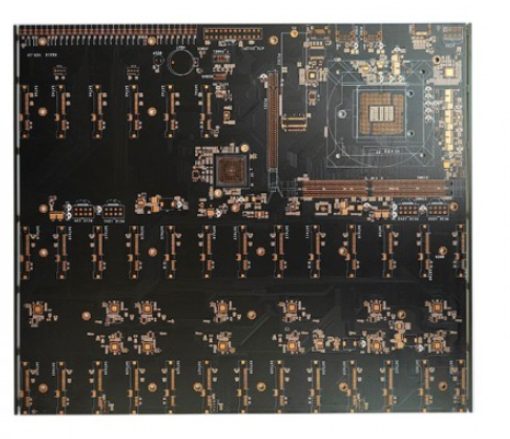

Recommended Spacing Guidelines for Multi-Layer PCBs

To minimize production challenges and ensure long-term reliability, adhere to the following spacing recommendations:

- Inner Layer Hole-to-Line/Copper Spacing:

- 4 Layers: Minimal impact; no strict spacing needed.

- 6 Layers: ≥6mil.

- 8 Layers: ≥7mil.

- 10 Layers or More: ≥8mil.

- Via-to-Via and Via-to-Line Spacing:

- Same Network Vias: ≥8mil (0.2mm).

- Different Network Vias: ≥12mil (0.3mm).

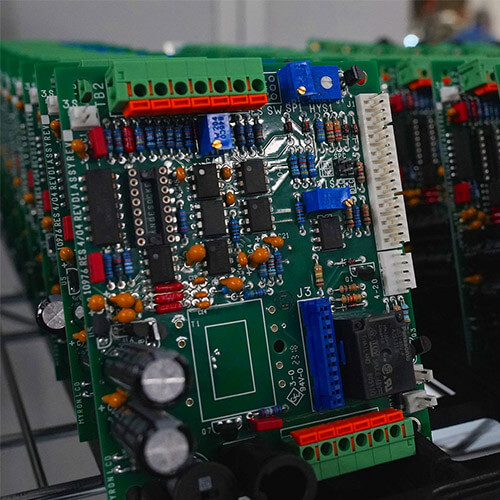

Strategies for Managing Close Via Spacing

- Optimize Hole Placement:

- Use design automation tools to identify and resolve potential spacing conflicts.

- Avoid routing dense lines near via clusters.

- Increase Hole Ring Size:

- Maximize the pad size within process constraints to provide more tolerance for deviations.

- Enhance Drilling Precision:

- Collaborate with PCB manufacturers to ensure state-of-the-art drilling equipment and processes.

- Layer Design Adjustments:

- Use staggered via designs where possible to reduce alignment dependencies between layers.

- Adhere to IPC Standards:

- Follow the IPC-2221 Level 2 standard, allowing ≤90° solder ring breaks but striving to minimize them.

Closely spaced vias are a common design challenge in multi-layer and high-speed PCB boards. Understanding the implications of tight spacing—such as drilling process inefficiencies, reduced solder ring size, and long-term reliability concerns—is essential. By adhering to recommended spacing guidelines, optimizing via placement, and collaborating with manufacturers, designers can enhance production yield, reduce costs, and ensure robust product per