High-Speed PCB Design Guide XI: How to Improve Testability

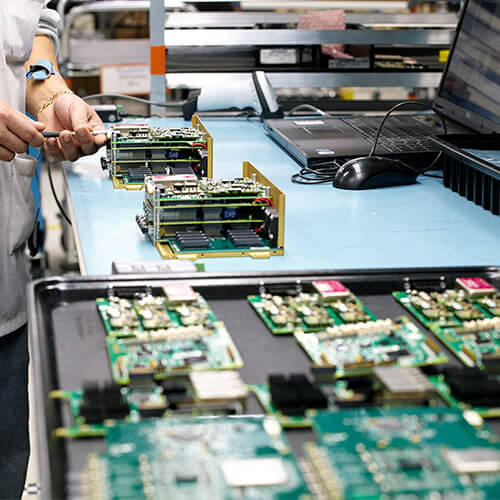

As electronic devices become increasingly miniaturized, advancements in component and wiring technologies have created new challenges for production testing. Highly integrated ICs, smaller insulation spacings, and limited access to circuit nodes have made traditional testing methods insufficient. To address these challenges, a design-for-testability (DFT) approach is essential to reduce testing costs and enhance production efficiency. This guide explores the principles, strategies, and best practices for improving PCB testability.

1. Understanding Testability

Testability refers to how easily a product’s functionality can be verified through testing. Key aspects include:

- Simplifying the method for determining whether the product meets technical specifications.

- Enhancing the ability to compile test programs.

- Ensuring comprehensive fault detection.

- Simplifying access to test points.

Achieving optimal testability requires collaboration between mechanical and electrical design teams during the product development stage.

2. Importance of Testability in Modern PCB Design

In the past, testing inefficiencies pushed defect identification to later stages. Today, the focus is on detecting faults early in the production cycle. Key reasons include:

- Reducing costs associated with late-stage defect detection.

- Addressing complex component issues, such as pre-installed software or programmable devices (e.g., Flash memory, ISP devices).

- Supporting lead-free processes and advanced mounting technologies like SMT and CMT.

Investing in test-friendly design minimizes the risk of undetected defects, reduces testing costs, and ensures robust product performance.

3. Role of Documentation in Enhancing Testability

Complete and accurate documentation is critical for effective testing. Essential documentation includes:

- Bill of materials (BOM).

- Circuit design data (CAD data).

- Component specifications and data sheets.

- Programming data for programmable components in industry-standard formats (e.g., Intel Hex, Motorola S-record).

Detailed documentation facilitates the creation of test programs, vector definitions, and failure pattern identification, ensuring thorough fault detection.

4. Mechanical Considerations for Improved Testability

Mechanical design affects testability just as much as electrical design. Best practices include:

- Ensuring precise positioning and dimensions of test points and locking holes.

- Avoiding test points with insufficient spacing or accessibility.

- Distributing test points evenly and maintaining at least 3 mm spacing from component edges.

- Designing for compatibility with probe bed adapters.

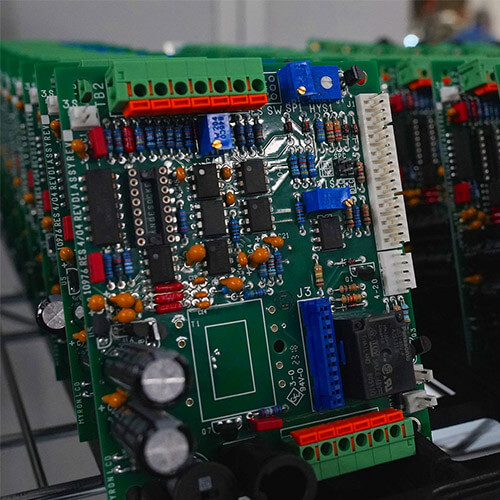

5. Electrical Design Best Practices

To ensure optimal testability, electrical designs must:

- Include mechanisms for isolating individual components during testing (e.g., inhibit input terminals).

- Provide enable or reset pins for all components, ensuring proper test initialization.

- Allow high-impedance states for nodes to avoid backdrive issues.

- Make unused pins accessible for potential future use or defect detection.

These measures prevent testing complications and ensure comprehensive fault identification.

6. Improving Testability in Production

Practical suggestions for optimizing testability:

Test Points:

- Minimum diameter: 0.88 mm (35 mil).

- Spacing: At least 2.5 mm between points.

- Uniform distribution across the PCB, preferably on the back of the plug-in board.

Locking Holes:

- Accurate positioning: ±0.05 mm.

- Diameter accuracy: ±0.076 mm.

Component Marking:

- Clear and consistent labeling of components, versions, and serial numbers.

- Barcode integration for tracking.

7. Flash Memory and Programmable Components

When testing programmable components (e.g., Flash, PLD, FPGA), consider:

- High-impedance states for components connected to the address and data buses during programming.

- Industry-standard programming data formats, such as Serial Vector Format (SVF) or JEDEC.

- Test signal generator capabilities for programming entire component chains.

8. Boundary Scan (JTAG) for Enhanced Testability

Boundary scan is a powerful method for improving testability in designs with limited physical test points. Key features include:

- Diagnosing short circuits and open circuits down to the pin level.

- Triggering automatic component tests via RunBIST commands.

- Reducing the need for extensive test vectors.

Implementing Boundary Scan:

- Ensure the circuit supports the IEEE-1149.1 standard.

- Provide test access pins: TDI, TDO, TCK, TMS, and test reset.

- Develop BSDL files for supported boundary scan functions and commands.

Boundary scan is particularly advantageous for circuits with complex ASICs and limited node access, complementing traditional testing methods for comprehensive fault detection.

KKPCB conducts research on special processing technologies such as ordinary double-sided boards, thick copper circuit boards, high-frequency circuit boards, HDI circuit boards, rigid-flexible circuit boards, FPC flexible boards, buried blind hole circuit boards, and IC carrier boards. Provides PCB design, PCB layout, PCB prototyping and PCB assembly services.