High-Speed PCB Design Guide 9: Mastering IC Packaging Characteristics

Electromagnetic interference (EMI) control is critical in high-speed PCB design, and one often-overlooked aspect is the influence of integrated circuit (IC) packaging. Incorporating decoupling capacitors within the IC package can effectively reduce EMI and enhance signal integrity. This guide delves into the role of IC packaging in EMI suppression, exploring the root causes of EMI, key IC package design considerations, and practical design rules to optimize performance.

Understanding the Source of EMI

EMI stems from transient signals in digital ICs, particularly during switching operations between logic high and low states. The high-frequency harmonics of square waves generated during these transitions contribute significantly to EMI.

The formula for the EMI emission bandwidth highlights the relationship between rise time and EMI frequency:

F=0.35TrF = \frac{0.35}{T_r}F=Tr0.35

Where:

- F is the EMI emission frequency in GHz.

- T_r is the signal rise or fall time in nanoseconds (ns).

Example:

- At a rise time (T_r) of 1 ns, EMI reaches 350 MHz.

- A faster rise time of 500 ps results in an EMI frequency of 700 MHz.

Moreover, poor control of capacitance and inductance in signal and power paths exacerbates EMI. Addressing these factors at the IC packaging level can greatly improve overall system EMI performance.

The Role of IC Packaging in EMI Suppression

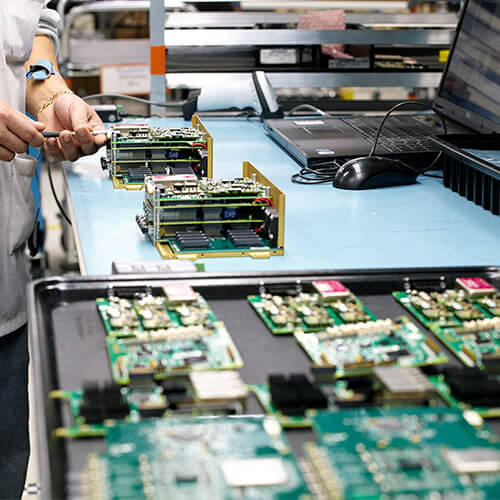

IC packaging connects the silicon-based chip to external circuits through internal PCBs and pins. Key design factors include:

- Connection Method:

- Wirebonding is commonly used to connect the silicon chip to the internal PCB. While cost-effective, it increases inductance due to larger current loop areas.

- Direct Bonding reduces inductance by connecting the chip directly to PCB pads but requires specialized low-CTE materials, increasing cost.

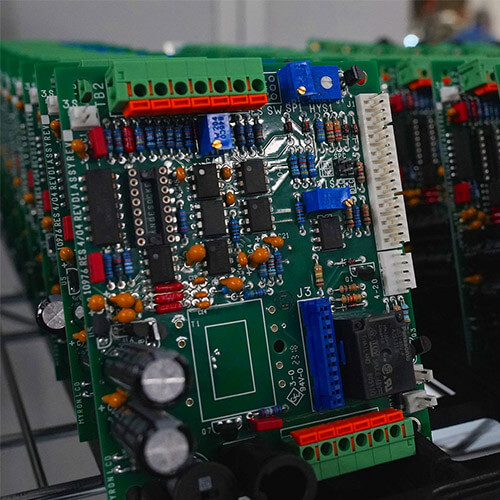

- Capacitance and Inductance Control:

- Smaller pitch surface-mount packages outperform through-hole leaded packages.

- Ball grid array (BGA) packages offer minimal lead inductance, making them ideal for high-speed designs.

- Pin Allocation:

- Allocate power and ground pins in pairs to reduce loop inductance.

- For signal integrity, pro

- vide adequate return paths (e.g., allocate one ground pin for every 4–6 signal pins).

11 Design Rules for EMI Control in IC Packaging

1. Choose Low-Inductance Packages

Opt for BGA or fine-pitch surface-mount ICs to minimize inductance.

2. Optimize Pin Allocation

- Pair power and ground pins.

- Allocate return paths within 4–6 signal pins.

3. Prioritize Capacitance Control

Design IC packages with sufficient capacitance between power, ground, and signal paths.

4. Use Decoupling Capacitors

Place capacitors within the IC package for high-frequency noise filtering.

5. Select Materials with Low CTE

For direct bonding, use substrates that match the thermal expansion of silicon chips.

6. Avoid Long Bonding Wires

Use direct connections or minimize wire length to reduce loop areas.

7. Incorporate Shielding

Design IC packages with Faraday cages or other shielding techniques for EMI containment.

8. Use Differential Signal Traces

Ensure symmetric pin allocation for differential signals to minimize EMI.

9. Minimize Output Driver Strength

Reduce output driver slew rates to control rise times and limit EMI emissions.

10. Implement Power Integrity Measures

Use advanced techniques like embedded decoupling or internal bypass capacitors for power noise control.

11. Verify Compatibility with PCB Design

Ensure IC pin arrangements align with PCB layout for effective power and ground distribution

Effective EMI suppression starts with the IC package design. By selecting ICs with optimized pin structures, low-inductance packages, and built-in EMI control features, engineers can simplify system-level EMI management.

Focusing on the integration of high-speed ICs with PCBs ensures better signal integrity, reduced EMI, and a more reliable electronic system.