EMI Solution in Multilayer PCB Design

There are many ways to solve the EMI problem. Modern EMI suppression methods include: using EMI suppression coatings, selecting appropriate EMI suppression components and EMI simulation design, etc. This article starts with the most basic PCB layout and discusses the role and design techniques of PCB layer stacking in controlling EMI radiation.

Power Bus

Placing capacitors of appropriate capacity near the power pins of the IC can make the IC output voltage jump faster. However, the problem does not end there. Due to the limited frequency response characteristics of the capacitor, it is impossible for the capacitor to generate the harmonic power required to drive the IC output cleanly over the full frequency band. In addition, the transient voltage formed on the power bus will form a voltage drop across the inductor of the decoupling path. These transient voltages are the main source of common-mode EMI interference. How should we solve these problems?

As far as the IC on our PCB circuit board is concerned, the power layer around the IC can be regarded as an excellent high-frequency capacitor, which can collect the energy leaked by the discrete capacitor that provides high-frequency energy for clean output. In addition, the inductance of an excellent power layer should be small, so that the transient signal synthesized by the inductance is also small, thereby reducing common-mode EMI.

Of course, the connection from the power layer to the IC power pin must be as short as possible. Because the rising edge of the digital signal is getting faster and faster, it is best to connect directly to the pad where the IC power pin is located. This needs to be discussed separately.

In order to control common-mode EMI, the power layer should help decoupling and have a low enough inductance. This power layer must be a pair of well-designed power layers. Some people may ask, how good is good? The answer to the question depends on the power layering, the material between the layers, and the operating frequency (i.e., the function of the IC rise time). Usually, the spacing of the power layer is 6mil, and the interlayer is FR4 material, then the equivalent capacitance of the power layer per square inch is about 75pF. Obviously, the smaller the layer spacing, the greater the capacitance.

There are not many devices with a rise time of 100 to 300ps, but according to the current development speed of IC, devices with a rise time in the range of 100 to 300ps will occupy a high proportion. For circuits with a rise time of 100 to 300ps, 3mil layer spacing will no longer be applicable to most applications. At that time, it is necessary to adopt layering technology with a layer spacing of less than 1mil and replace FR4 dielectric materials with materials with very high dielectric constants . Now, ceramics and ceramic plastics can meet the design requirements of circuits with a rise time of 100 to 300ps.

Although new materials and new methods may be adopted in the future, for today’s common 1 to 3ns rise time circuits, 3 to 6mil layer spacing and FR4 dielectric materials, it is usually enough to handle high-end harmonics and make transient signals low enough, that is, common-mode EMI can be reduced very low. The PCB layer stacking design example given in this article will assume that the layer spacing is 3 to 6mil.

Electromagnetic shielding

From the perspective of signal routing, a good layering strategy should be to place all signal routing on one or several layers, which are close to the power layer or ground layer. For power supply, a good layering strategy should be that the power layer is adjacent to the ground layer, and the distance between the power layer and the ground layer is as small as possible. This is what we call the “layering” strategy.

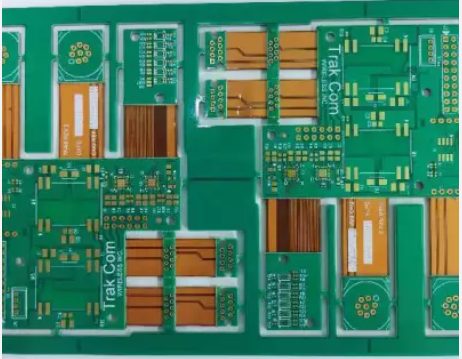

PCB Stack-up

What kind of stacking strategy helps shield and suppress EMI? The following layered stacking scheme assumes that the power current flows on a single layer, and the single voltage or multiple voltages are distributed in different parts of the same layer. The case of multiple power layers will be discussed later.

4-layer board

There are several potential problems with 4-layer board design. First, for a traditional 62mil thick 4-layer board, even if the signal layer is on the outer layer and the power and ground layers are on the inner layer, the spacing between the power layer and the ground layer is still too large.

If cost is the first priority, you can consider the following two alternatives to the traditional 4-layer board. Both solutions can improve the EMI suppression performance, but they are only applicable when the component density on the board is low enough and there is enough area around the components (to place the required power copper layer).

The first is the preferred solution, where the outer layers of the PCB are all ground layers, and the two middle layers are signal/power layers. The power supply on the signal layer is routed with a wide line, which can make the path impedance of the power supply current low, and the impedance of the signal microstrip path is also low. From the perspective of EMI control, this is the best 4-layer PCB structure available. The second solution uses power and ground on the outer layers, and signals on the middle two layers. This solution is less improved than the traditional 4-layer board, and the inter-layer impedance is as poor as the traditional 4-layer board.

If you want to control the trace impedance, the above stacking schemes must be very careful to arrange the traces under the power and ground copper islands. In addition, the copper islands on the power or ground layer should be interconnected as much as possible to ensure DC and low-frequency connectivity.

6-layer board

If the density of components on a 4-layer board is relatively high, a 6-layer board is preferred. However, some stacking schemes in a 6-layer board design do not provide adequate shielding of electromagnetic fields and have little effect on reducing transient signals on the power bus. Two examples are discussed below.

In the first example, the power supply and ground are placed on the 2nd and 5th layers respectively. Since the power supply copper has high impedance, it is very unfavorable to control common mode EMI radiation. However, from the perspective of signal impedance control, this method is very correct.

In the second example, the power supply and ground are placed on the 3rd and 4th layers respectively. This design solves the power supply copper impedance problem. Due to the poor electromagnetic shielding performance of the 1st and 6th layers, differential mode EMI increases. If the number of signal lines on the two outer layers is the least and the routing length is very short (shorter than 1/20 of the wavelength of the highest harmonic of the signal), this design can solve the differential mode EMI problem. Filling the component-free and routing-free areas on the outer layer with copper and grounding the copper-clad areas (at intervals of 1/20 wavelength) will suppress differential mode EMI particularly well. As mentioned earlier, the copper-clad areas should be connected to the internal ground layer at multiple points.

The general high-performance 6-layer board design generally uses the 1st and 6th layers as ground layers, and the 3rd and 4th layers for power and ground. Since there are two layers of dual microstrip signal lines in the middle between the power layer and the ground layer, the EMI suppression capability is excellent. The disadvantage of this design is that there are only two routing layers. As mentioned earlier, if the outer layer routing is short and copper is laid in the non-routing area, the same stacking can be achieved with a traditional 6-layer board.

Another 6-layer board layout is signal, ground, signal, power, ground, signal, which can achieve the environment required for advanced signal integrity design. The signal layer is adjacent to the ground layer, and the power layer and ground layer are paired. Obviously, the disadvantage is that the stacking of the layers is unbalanced.

This usually causes troubles in processing and manufacturing. The solution to the problem is to fill all the blank areas of the third layer with copper. After copper filling, if the copper density of the third layer is close to that of the power layer or the ground layer, the board can be loosely regarded as a structurally balanced circuit board. The copper-filled area must be connected to the power supply or ground. The distance between the connecting vias is still 1/20 wavelength. It is not necessary to connect everywhere, but ideally it should be connected.

10-layer board

Since the insulation isolation layer between multilayer PCB boards is very thin, the impedance between layers of 10 or 12-layer circuit boards is very low. As long as there are no problems with layering and stacking, excellent signal integrity can be expected. It is difficult to manufacture 12-layer boards with a thickness of 62mil, and there are not many manufacturers that can process 12-layer boards.

Since there is always an insulating layer between the signal layer and the loop layer, it is not optimal to allocate the middle 6 layers to signal lines in a 10-layer board design.

This design provides a good path for signal current and its loop current. The proper routing strategy is that the first layer is routed in the X direction, the third layer is routed in the Y direction, the fourth layer is routed in the X direction, and so on. Intuitively, the first layer and the third layer are a pair of layer combinations, the fourth layer and the seventh layer are a pair of layer combinations, and the eighth layer and the tenth layer are the last pair of layer combinations. When the routing direction needs to be changed, the signal line on the first layer should go through the “via” to the third layer before changing direction. In practice, it may not always be possible to do this, but as a design concept, it should be followed as much as possible.

Similarly, when the signal routing direction changes, it should be routed from the 8th and 10th layers or from the 4th layer to the 7th layer through vias. This routing ensures the tightest coupling between the forward path and the loop of the signal. For example, if the signal is routed on the 1st layer, the loop is on the 2nd layer and only on the 2nd layer, then even if the signal on the 1st layer is transferred to the 3rd layer through a “via”, its loop is still on the 2nd layer, thus maintaining the characteristics of low inductance, large capacitance and good electromagnetic shielding performance.

What if the actual routing is not like this? For example, if the signal line on the first layer goes to the tenth layer through a via, the loop signal has to find the ground plane from the ninth layer, and the loop current needs to find the nearest ground via (such as the ground pin of a resistor or capacitor). If such a via happens to exist nearby, you are really lucky. If there is no such via available, the inductance will increase, the capacitance will decrease, and EMI will definitely increase.

When the signal line must leave the current pair of wiring layers to other wiring layers through vias, a ground via should be placed next to the via so that the loop signal can smoothly return to the appropriate ground layer. For the layered combination of the 4th and 7th layers, the signal loop will return from the power layer or the ground layer (that is, the 5th or 6th layer) because the capacitive coupling between the power layer and the ground layer is good and the signal is easy to transmit.

Multi-power layer design

If two power layers of the same voltage source need to output large currents, the circuit board should be laid out into two sets of power layers and ground layers. In this case, an insulating layer is placed between each pair of power layers and ground layers. In this way, we get two pairs of power buses with equal impedance that divide the current equally as we expect. If the stacking of power layers causes unequal impedance, the current division will be uneven, the transient voltage will be much larger, and EMI will increase dramatically.

If there are multiple power supply voltages with different values on the circuit board, multiple power supply layers are required accordingly. Remember to create paired power and ground layers for different power supplies. In both cases, when determining the location of paired power and ground layers on the circuit board, keep in mind the manufacturer’s requirements for balanced structures.

Summarize

Since most engineers design traditional PCBs with a thickness of 62mil and no blind or buried vias, the discussion of PCB layering and stacking in this article is limited to this. For PCBs with too large a difference in thickness, the layering scheme recommended in this article may not be ideal. In addition, the processing process of PCBs with blind or buried vias is different, so the layering method in this article is not applicable.

In circuit board design, the thickness, via process and number of circuit board layers are not the key to solving the problem. Excellent layer stacking is the key to ensure bypass and decoupling of the power bus, minimize transient voltage on the power layer or ground layer, and shield the electromagnetic field of the signal and power supply. Ideally, there should be an insulating isolation layer between the signal routing layer and its loop ground layer, and the spacing between paired layers (or more than one pair) should be as small as possible. Based on these basic concepts and principles, a circuit board that always meets the design requirements can be designed. Now that the rise time of ICs is very short and will be shorter, the technology discussed in this article is essential to solving the EMI shielding problem.